Product Summary

The IDT74LVC125ADC is a quadruple bus buffer gate. The IDT74LVC125ADC is built using advanced dual metal CMOS technology. The IDT74LVC125ADC features independent line drivers with 3-state outputs. Each output is disabled when the associated outputenable (OE) input is high. To ensure the high impedance state during power up or power down, OE should be tied to Vcc through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Parametrics

IDT74LVC125ADC absolute maximum ratings: (1)VTERM Terminal Voltage with Respect to GND: –0.5 to +6.5 V; (2)TSTG Storage Temperature: –65 to +150 ℃; (3)IOUT DC Output Current: –50 to +50 mA; (4)IIK Continuous Clamp Current: –50 mA; (5)ICC Continuous Current through each: ±100 mA.

Features

IDT74LVC125ADC features: (1)0.5 MICRON CMOS Technology; (2)ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0); (3)VCC = 3.3V ± 0.3V, Normal Range; (4)VCC = 2.7V to 3.6V, Extended Range; (5)CMOS power levels (0.4μ W typ. static); (6)Rail-to-Rail output swing for increased noise margin; (7)All inputs, outputs, and I/Os are 5V tolerant; (8)Supports hot insertion; (9)Available in SOIC, SSOP, and TSSOP packages.

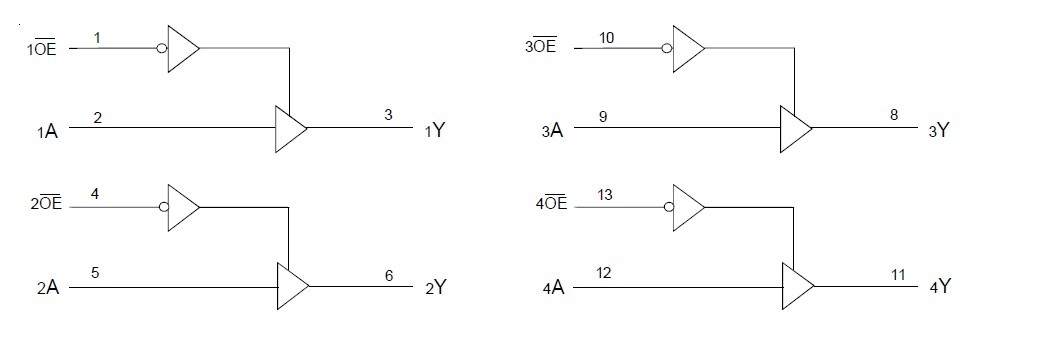

Diagrams

|

IDT7005 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L15J |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15J8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))