Product Summary

The EDS1216AATA-75-E is a 128M bits SDRAM organized as 2,097,152 words × 16 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. It is packaged in 54-pin plastic TSOP (II).

Parametrics

EDS1216AATA-75-E absolute maximum ratings: (1)Voltage on any pin relative to VSS VT: -0.5 to VDD + 0.5 (≤ 4.6 (max.))V; (2)Supply voltage relative to VSS] VDD: -0.5 to +4.6 V; (3)Short circuit output current IOS: 50 mA; (4)Power dissipation PD: 1.0 W; (5)Operating ambient temperature TA: 0 to +70 ℃; (6)Storage temperature Tstg: -55 to +125 ℃.

Features

EDS1216AATA-75-E features: (1)3.3V power supply; (2)Clock frequency: 133MHz (max.); (3)Single pulsed /RAS; (4)×16 organization; (5)4 banks can operate simultaneously and independently; (6)Burst read/write operation and burst read/single write operation capability; (7)Programmable burst length (BL): 1, 2, 4, 8, full page; (8)2 variations of burst sequence; (9)Programmable /CAS latency (CL): 2, 3; (10)Byte control by UDQM and LDQM; (11)Refresh cycles: 4096 refresh cycles/64ms.

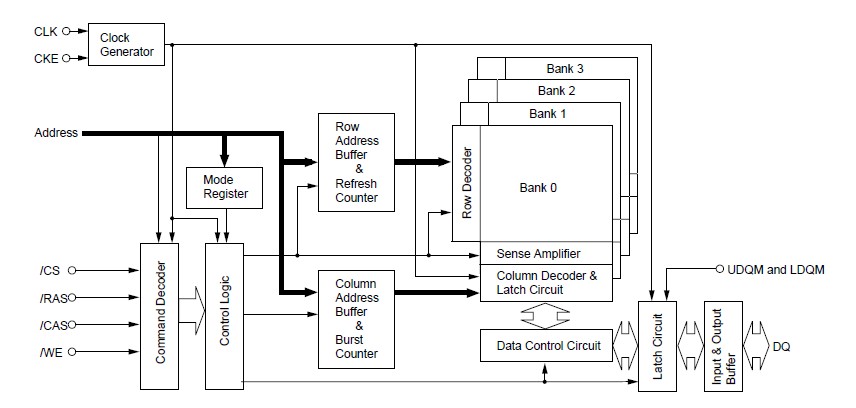

Diagrams

|

EDS1216AABH |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EDS1216AATA |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EDS1216AHTA |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EDS1216CABH |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EDS1232AABB |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EDS1232AASE |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))